티스토리 뷰

Bulk Potential

$E_{i}$ 와 $E_{F}$의 차이에서 Bulk Potential을 사용할 수 있습니다.

두 에너지 차이를 $q\phi _{B}$라고 합니다.

p 타입에서 $E_{F}$가 더 아래에 있으므로 양수가 나오며 n 타입에선 음수가 나올 것입니다.

Surface Potential

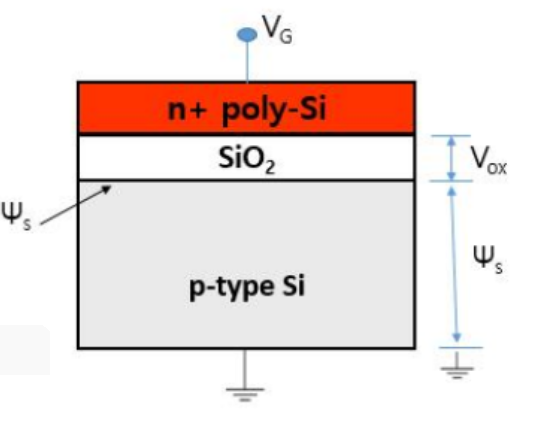

Oxide와 반도체의 계면 퍼텐셜(surface potential)을 $\phi _{s}$ 라고 합니다.

이는 직관적으로 에너지 밴드가 얼마나 굽었는지를 나타낸다고 생각하면 될 것 같습니다.

Si에서 절연체 표면까지 에너지 밴드가 휘어질 때가 있는데 그 차이를 말합니다.

다음 그림에서 $q\phi_{s}$ 를 보면 이해할 수 있습니다.

(아래 그림에서 $\phi<0$ 입니다.)

때문에 기울어진 에너지 밴드일 때 $\phi$는 0이 아닙니다.

이전에 말했던 Flat-Band Voltage를 가한다면 에너지 밴드의 형태가 평평하게 나타날 것이고

이때 surface potential은 0입니다.

[전자소자] MOS Capacitor Flat-Band Condition

MOS Capacitor 소개 MOSFET를 배우기 앞서 MOSFET의 일부라고도 할 수 있는 MOS Capacitor 에 대해 다뤄보겠습니다. MOS(metal oxide semiconductor) 에서 Metal 즉 Gate 부분은 주로 degenerately doped poly-Si를 사용합니다.

studentstory.tistory.com

Voltage drops in the MOS

Gate 전압을 $V_{G}$ 라고 하고 이를 나타내봅시다.

Flat Band Condition일 때 (metal과 반도체의 일함수가 같을 때)

다음 그림과 같이 $V_{G}$는 절연체에 걸린 전압과 Si body에 걸린 전압의 합이라 생각할 수 있습니다.

다만 일반적인 경우 Flat Band Voltage를 걸어야 Flat Band Condition이 되므로

$V_{G}=V_{FB}+V_{OX}+\phi _{s}$ 라 할 수 있습니다.

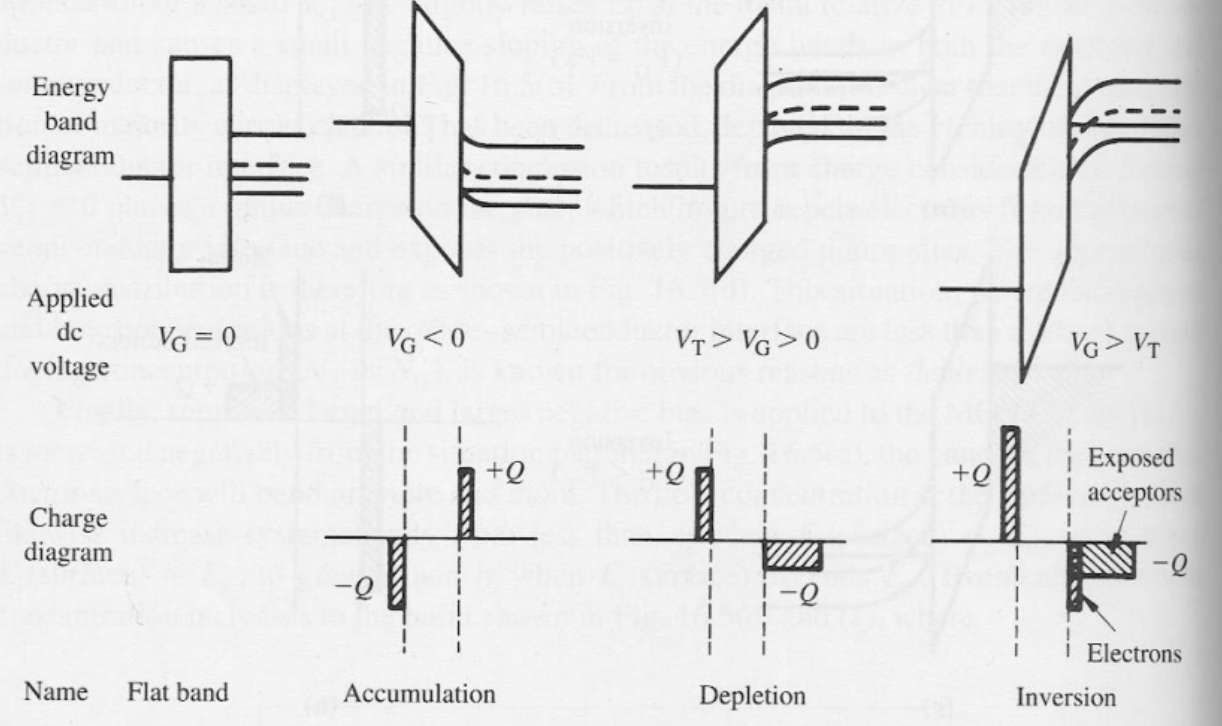

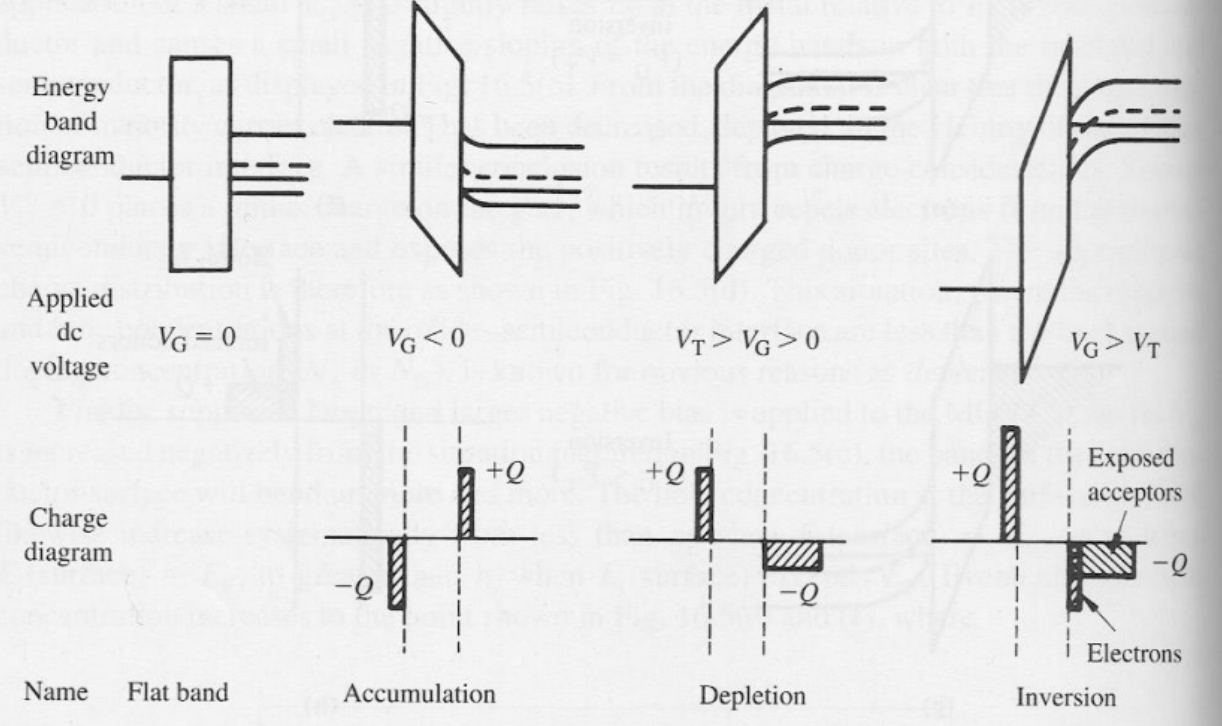

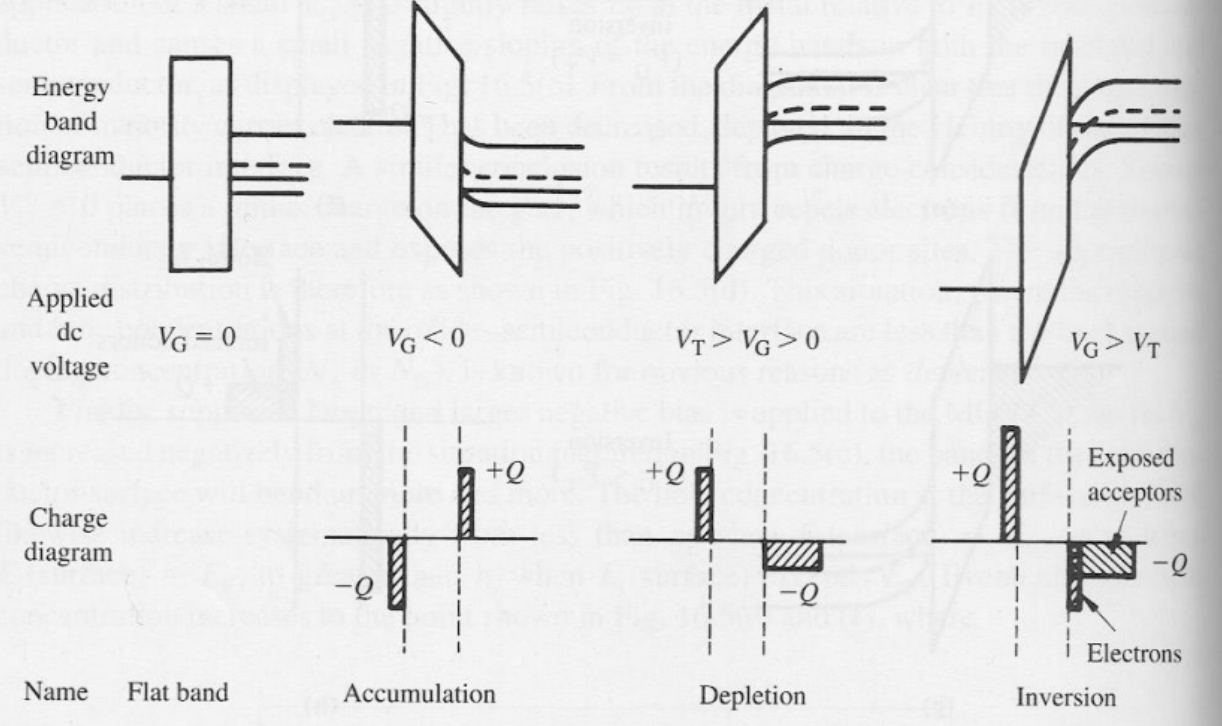

p-type Si 를 가진 MOS가 Flat band condition의 상황이라 가정하고

$V_{G}$에 따라 어떤 밴드 다이어그램이 나타나는지 생각해봅시다.

$V_{G}$ 가 음수일 때 Accumulation

이전에 배웠다시피 절연체의 에너지밴드가 기울어진 형태를 보입니다.

쉽게 생각해 Si 부분이 게이트에 비해 큰 전압이 걸리고 에너지 밴드가 비교적 아래로 내려간다고 생각하면

다음과 같이 에너지 밴드는 휘게 될 것입니다.

또한 이상적인 절연체이므로 전류는 흐르지 않으며 역시 페르미 레벨도 일정한 형태를 보입니다.

charge diagram을 보면 metal 부분은 음전하(전자)가 몰리고 Si 부분은 양전하가 축적됩니다.

p-type인 Si에 정공(hole)이 많이 존재하며 표면에 축적되었다고 생각하면 좋을 것 같습니다.

때문에 이러한 조건에서 Accumulation 이라 합니다.

$V_{G}$ 가 양수일 때 (임계전압보다는 작은) Depletion

사실 임계전압을 아직 정의하지 않았지만 이러한 경우를 생각해보면 방금 경우와 반대의 형태를 띄게 됩니다.

역시나 페르미 레벨 $E_{F}$는 일정합니다.

charge diagram을 보면 metal 부분은 양전하가 몰렸고 부호만 다를 뿐 앞선 경우와 형태가 비슷합니다.

다만 Si에는 방금과는 다른 모양인데요. hole이 다수캐리어인 p-type 이기 때문입니다.

즉 전자가 축적된 것이 아니라 hole이 반대로 밀려 음이온만 남은 것입니다.

때문에 음이온으로 인한 전하 -Q가 존재하는 것입니다.

이렇게 이온화로 Depletion 영역이 생겨 이를 Depletion이라 합니다.

$V_{G}$ 가 임계전압 $V_{T}$보다 클 때 Inversion

이때는 두번째 경우에서 과한 경우라고 생각해봅니다.

다만 다른 점은 페르미 레벨 $E_{F}$와 $E_{i}$가 교차되었다는 것입니다.

때문에 절연체와 Si 부근은 n-type과 같은 에너지 밴드를 가지게 되고 여기엔 전자가 존재함을 알 수 있습니다.

charge diagram에서 굉장히 특이한 형태를 보이는데 전자에 의한 전하가 추가로 존재함을 알 수 있습니다.

n 타입 처럼 보이듯 반전되어 Inversion이라 부릅니다.

이렇게 세 가지 경우를 살펴보았는데, 다만 처음에 Flat band 를 조건으로 알아본 것이었습니다.

때문에 처음부터 Flat band가 아닌 경우는 전압이 0이 아닌 $V_{FB}$라고 생각해야 할 것입니다.

무슨 말이냐면 위에서는 $V_{G}=0$ 에서 Flat band라고 생각했지만

$V_{G}=V_{FB}$에서 Flat band 라고 생각해야 한다는 뜻입니다.

결국 Accumulation은 $V_{G}<V_{FB}$

Depletion은 $0<V_{G}<V_{T}$

Inversion은 $V_{G}>V_{T}$ 라는 것입니다.

Flat band condition을 처음 정의할 때는 왜 알아야하는지, Flat band voltage를 어디에 쓰는지 알 수 없었습니다. 하지만 Flat band부터 생각하며 더 쉽게 게이트 전압에 따른 형태를 떠올릴 수 있었습니다.

다음 글에서는 세 가지 경우를 수식적으로 알아보겠습니다.

'전기전자공학 > 반도체 소자 공학 (물리전자|전자소자)' 카테고리의 다른 글

| [전자소자] 모스펫의 subthreshold condition 정리 (0) | 2024.05.19 |

|---|---|

| [전자소자] Poly-Si Gate Depletion (0) | 2024.03.21 |

| [전자소자] MOS게이트 전압 Vg(for depletion, threshold, inversion) (0) | 2024.03.13 |

| [전자소자] MOS Capacitor Flat-Band Condition (1) | 2024.03.06 |

| [물리전자] PN 다이오드 I-V 특성, Ideal & Real 다이오드 전류 특성 (0) | 2023.12.17 |

| [물리전자] PN Junction depletion 영역 (Width, Capacitance) (1) | 2023.12.17 |

| [물리전자] PN junction Forward Bias에서 캐리어 농도 (Excess Carrier Concentration) (0) | 2023.12.04 |

| [물리전자] 이상적인 다이오드 원리 설명 (1) | 2023.12.04 |

- Total

- Today

- Yesterday

- 리브모바일

- 리브엠

- f-94w

- 시계 줄

- 오블완

- 알뜰 요금제

- 카카오페이

- 티스토리챌린지

- 알리익스프레스

- 알뜰폰요금제

- f-91w

- 파스타

- 북문

- 방향장

- mealy

- 문서 스캔

- 계산방법

- Liiv M

- 메쉬 밴드

- 경북대

- 네이버페이

- 할인

- 배송기간

- a모바일

- 10만포인트

- 밀리머신

- 카시오

- 교체

- 무어머신

- 맛집

| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | ||||

| 4 | 5 | 6 | 7 | 8 | 9 | 10 |

| 11 | 12 | 13 | 14 | 15 | 16 | 17 |

| 18 | 19 | 20 | 21 | 22 | 23 | 24 |

| 25 | 26 | 27 | 28 | 29 | 30 | 31 |